## Processor Data Path and Control

CIT 595 Spring 2007

## What Do We Know?

## Already discovered:

- Gates (AND, OR..)

- Combinational logic circuits (decoders, mux)

- Memory (latches, flip-flops)

- Sequential logic circuits (state machines)

- Simple processors (programmable traffic sign)

## What's next?

Apply all this to build a working processor

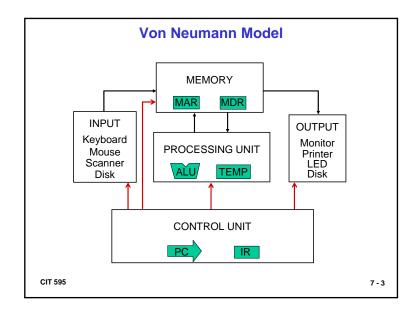

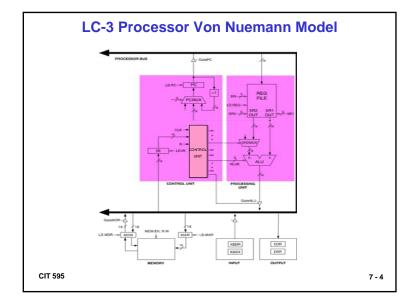

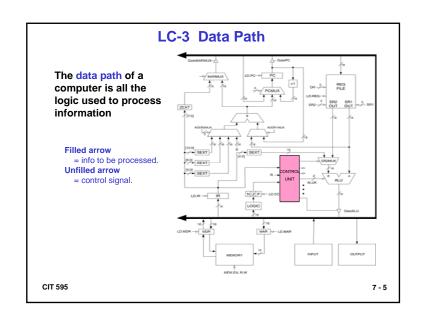

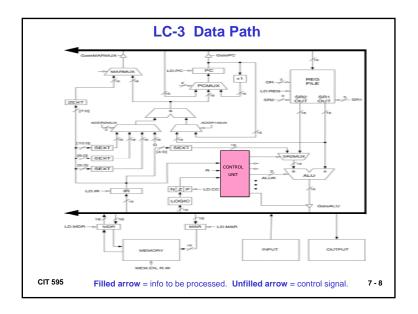

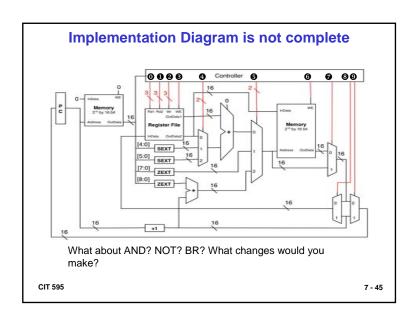

# **Data Path Components**

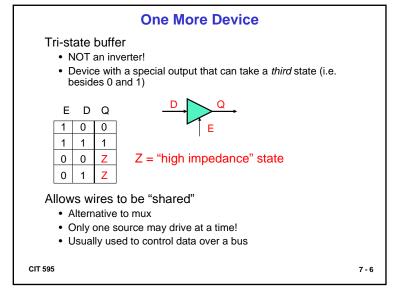

#### Global bus

- · Set of wires that carry 16-bit signals to many components

- Inputs to bus are controlled by triangle structure called tri-state devices

- > Place signal on bus when enabled

- > Only one (16-bit) signal should be enabled at a time

- > Control unit decides which signal "drives" the bus

- · Any number of components can read bus

- > Register only captures bus data if write-enabled by the control unit

#### Memory and I/O

- · Control signals and data registers for memory and I/O devices

- Memory: MAR, MDR (also control signal for read/write)

- · Input (keyboard): KBSR, KBDR

- · Output (text display): DSR, DDR

## **Data Path Components** (cont.)

#### ALU

- Input: register file or sign-extended bits from IR (immediate field)

- · Output: bus; used by...

- > Condition code registers

- > Register file

- ➤ Memory and I/O registers

#### Register File

- Two read addresses, one write address (3 bits each)

- Input: 16 bits from bus

- > Result of ALU operation or memory (or I/O) read

- · Outputs: two 16-bit

- > Used by ALU, PC, memory address

- > Data for store instructions passes through ALU

CIT 595 7 - 9

# **Data Path Components** (cont..)

#### Condition Code Logic

- Looks at value (from ALU) on bus and generates N, Z, P signals

- N,Z,P Registers are set only when control unit enables them

#### **Control Unit**

- For each stage in instruction processing decides:

- ➤ Who drives the bus?

- ➤ Which registers are write enabled?

- ➤ Which operation should ALU perform?

Lets Look at Instruction Processing next..

CIT 595 7 - 11

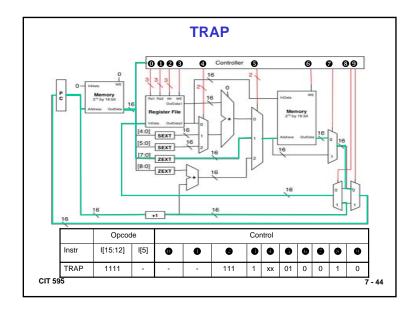

## **Data Path Components** (contd..)

#### PC and PCMUX

- Three inputs to PC, controlled by PCMUX

- 1. Current PC plus 1 (normal operation)

- 2. Adder output (BR, JMP, ...)

- 3. Bus (TRAP)

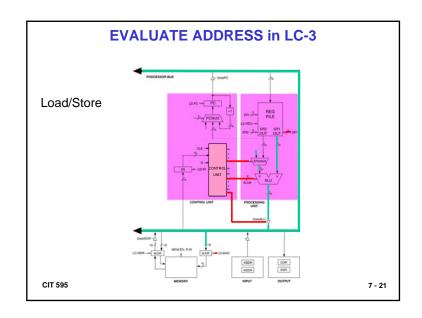

#### MAR and MARMUX

- · Some inputs to MAR, controlled by MARMUX

- 1. Zero-extended IR[7:0] (used for TRAP; more later)

- 2. Adder output (LD, ST, ...)

CIT 595 7 - 10

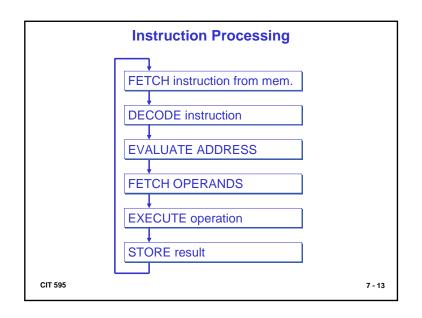

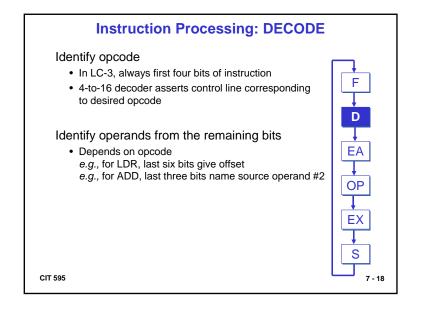

#### Instructions

#### Fundamental unit of work

#### Constituents

- · Opcode: operation to be performed

- Operands: data/locations to be used for operation

#### Encoded as a sequence of bits (just like data!)

- Sometimes have a fixed length (e.g., 16 or 32 bits)

- Atomic: operation is either executed completely, or not at all

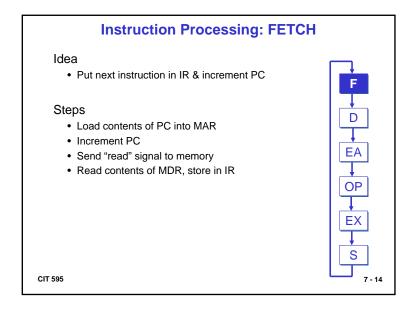

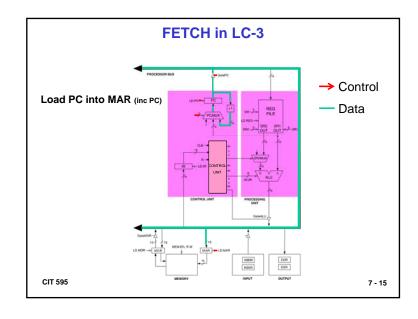

## **Time to Complete One Instruction**

- It takes fixed number of clock ticks (repetition of rising or falling edge) to execute each instruction

- ➤ The time interval between ticks is known as *clock cycle*

- > Thus instruction performance is measured in clock cycles

- Hence the clock sequences each phase of an instruction by raising the right signals as the right time

- So what determines the time between ticks i.e. the length of the clock cycle?

## **Clocking Methodology**

- Defines when signals can be read and when they can be written

- It is important to specify the timing of reads and writes because, if a value is written at the same time it is read, the value of read could be old, new or mix of both

- All values are stored on clock edge (edge-triggered) i.e. within a defined interval of time (length of the clock cycle)

- In a processor, since only memory elements can store values this means that

- Any collection of combinational logic must have its inputs coming from a set of memory elements and its outputs written into a set of memory elements

CIT 595 7 - 33

# Element Combinational Logic

element 2 defines the length of the clock cycle

Memory

• The time necessary for the signals to reach memory

**Clocking Methodology (contd..)**

• The length of the clock cycle is determined as follows:

> i.e. minimum clock cycle time must be at least as great as the maximum propagation delay of the circuit

CIT 595 7 - 34

#### How does the control unit work?

## Two approaches:

- Hardwired Control

- Microprogrammed Control

CIT 595 7 - 35

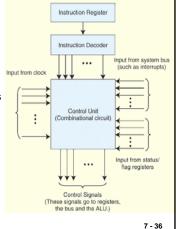

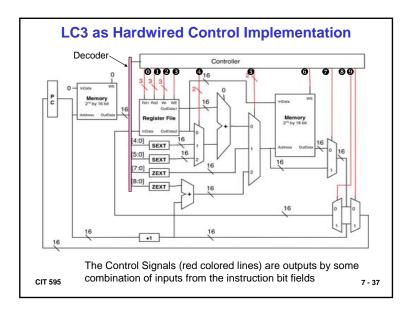

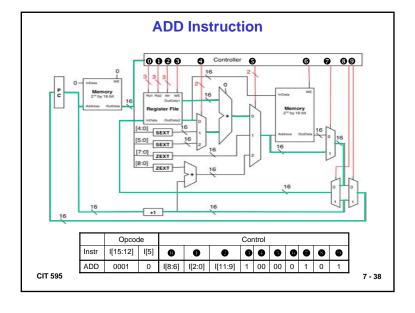

## **Approach I: Hardwired Control**

#### **Hardwired Control**

- Directly connects the control lines to actual machine instructions

- > The instructions are divided into fields, and bits in the fields are connected to input lines that drives the various digital logic components

- The control signals are some combination of the instruction bit plus other signals such as interrupts, or condition codes from previous instruction

Memory

2

CIT 595

7 - 30

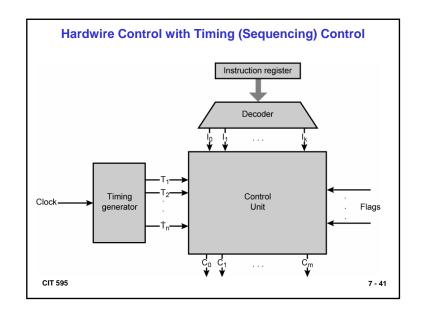

#### **Sequencing the Stages in Hardwired Implementation**

- The combination Control Unit set all the control lines needed by an instruction

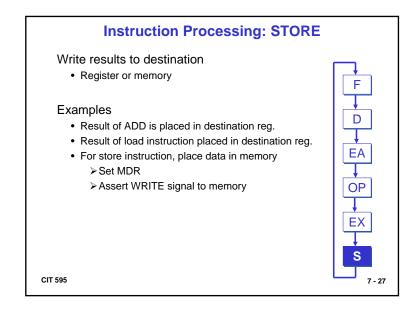

- How do we ensure that we sequence through Instruction cycle i.e. F->D->EA->OP->EX->S?

- We connect the clock to a synchronous counter and the counter to the decoder

- The decoder output enabled is based on counter outputs (i.e. which cycle you are in)

- The decoder output is then used as enable signal (gating) to enable only certain control signals during a particular cycle

- Note: the diagram does not show sequencing logic to avoid cluttering the diagram

CIT 595 7 - 39

# Sequencing Instruction Stages in Hardwired Implementation (contd..)

#### Example:

- Suppose the max. number of cycles an instruction takes is 8

- Then we would have 3-bit counter whose outputs are fed into 3 x 8 decoder

- The output of the decoder, T<sub>0</sub> to T<sub>7</sub> are enable based on count i.e.

$FT_0 = 1$  when count = 000 (cycle 0), all others are disabled

$T_7 = 1$  when count = 111(cycle 7), all others are disabled

- The decoder output that is enabled used to define the behavior in a particular cycle

- If < 8 clock cycles are required by another instr., then the counter is reset back to 0 (so the next instruction can properly function as well)

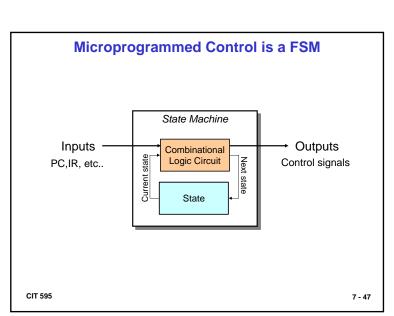

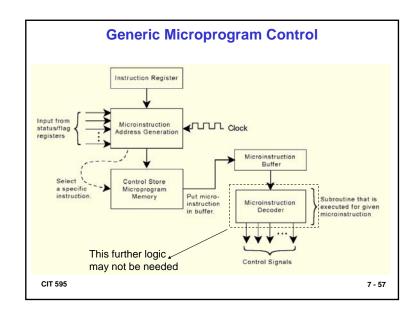

## **Approach II: Microprogrammed Control**

- In microprogrammed control, each machine instruction is in turn implemented by a series of microinstructions

- Machine instructions are the input for a microprogram that converts the 1s and 0s of an instruction into control signals

- The microinstructions are often stored in firmware or read only memory, which is also called the control store

- · Microprogram is also known as Microcode in some literature

- Microprogram Control is essentially a Finite State Machine

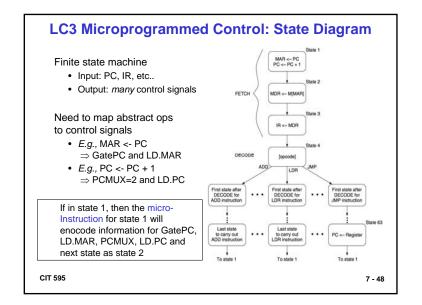

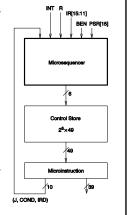

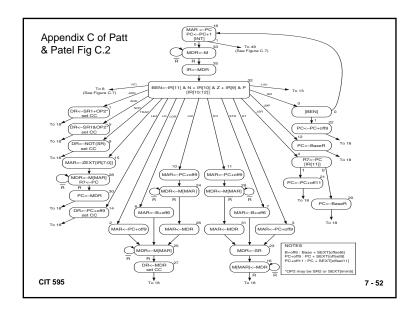

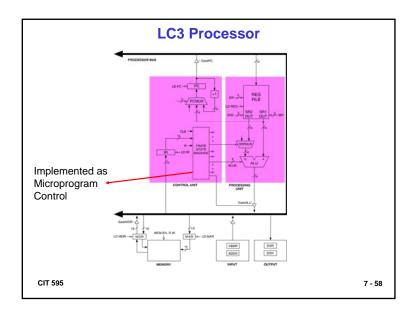

## **LC3 Implemented using Microprogram Control**

- The behavior of LC-3 during a given clock cycle is completely described by the 49 bit microinstruction

- 39 control signals to assert datapath components

- 10 signals + 9 other to determine the control signals for the next clock cycle

- Each phase of instruction cycle may require more than one microinstruction

- Hence a microinstruction is retrieved during each clock cycle

**CIT 595**

Microprogram Control

7 - 49

## LC3 Implemented using Microprogram Control (contd..)

- All possible processor behavior (state) is stored into memory called Control Store

- i.e. each location stores one microinstruction

- There are 52 possible microinstructions (states) that can describe LC3's behavior

- Hence need a 6-bit address to lookup the control store

- The microsequencer produces the 6 bit address from combination of 10 bits of Microinstruction + 9 bit additional info, which will correspond to the next behavior of the processor

**CIT 595**

Microprogram Control

7 - 5

#### LC3 Microprogram: Control Signals for Current State

| CURR<br>STATE | GATE  |    |     | LD  |    |     |   |        | MUX |     |               | MISC  |         |       |          |     |           |

|---------------|-------|----|-----|-----|----|-----|---|--------|-----|-----|---------------|-------|---------|-------|----------|-----|-----------|

|               | MARMX | PC | ALU | MDR | PC | REG | C | I<br>R | MAR | MAR | PC            | SR2   | SR1     | ALUK  | DR       | R.W | MEM<br>EN |

| 18            | 0     | 1  | 0   | 0   | 1  | 0   | 0 | 0      | 1   | х   | 0<br>(PC + 1) | х     | х       | х     | х        | 0   | 0         |

| 1             | 0     | 0  | 1   | 0   | 0  | 1   | 1 | 0      | 0   | ×   | x             | IR(5) | IR[8:6] | (ADD) | IR[11:9] | 0   | 0         |

The table above provides the control signal values (some of the 39 signals) for two states (18, 1)

State 18: Is performing part of the FETCH stage

State 1: Is performing stages OP-EX-STORE for ADD inst

#### Note:

- Assume all Register and Memory Read/Write signal are set 0 unless in case of write (i.e. set to 1)

- Also there is no need of timing circuit like in hardwired control, as each signal behavior is defined for every clock cycle

CIT 595 7 - 53

# LC3 Microprogram: Next State (contd..)

Depends on (contd..):

- INT: To indicate interrupt from another program or device, Only tested if in state 18 (because that is before the start of an instruction cycle)

- R: indicate the end of memory operation

- IR[15:11]: current opcode

- PSR[15]: processor executing in supervisor or user mode

- BEN: indicates whether or not a branch should be taken

CIT 595 7 - 55

## LC3 Microprogram: Next State

#### Depends on:

- 10 bits of current microinstruction

- J (6-bits): encodes the next state (mostly likely states of the possible next states)

- COND (3-bits): field indicates special tests that must occur to compute the true next state

- > 0 Unconditional (that next state is the encoded state)

- ▶1 Memory Read

- ≥2 Branch

- ➤ 3 Addressing Mode (for JSR and JSRR instructions)

- ≥5 Interrupt Test

- IRD (1-bit): If set to IRD = 1, ignore J and COND. This only happens in state 32 and as we want to use the bits from the IR to select the next state

CIT 595 7 - 54

## **LC3 Next State Example**

| CURR<br>STATE | J  | COND | IRD | POSSIBLE<br>NEXT STATE<br>(depends<br>also on 9<br>other Bits) |

|---------------|----|------|-----|----------------------------------------------------------------|

| 18            | 33 | 5    | 0   | 33,49                                                          |

| 1             | 18 | 0    | 0   | 18                                                             |

| 32            | 0  | 0    | 1   | 0-15                                                           |

- State 18: Most likely next state is 33 but need to check for INT (COND = 5). If INT = 1, Next State = 49

- State 1: Next State is just 18 (this because you are done finishing ADD instr and want to start a new instr. Cycle)

- State 32: J and COND ignored as IRD = 1, 0 − 15 are your next possible states

## Hardwired vs. Microprogrammed

## Complexity

There is an extra level of instruction interpretation in microprogrammed control, which makes it slower than hardwired control

## Flexibility

- Instruction and Control Logic are tied together in hardwired control, which makes it difficult to modify

- New instructions can be easily added by only making changes to the microprogram in microprogrammed control implementation