Virtuální paměť

Rámec (Frame) je stejně veliký prostor jako stránka (Page) = 4k |

|

Každý odkaz na paměť obsahuje virtuální adresu:

|

Ta se transformuje přes tabulku obsazení rámců na reálnou adresu |

P000 Architektura počítačůObsahpředchozí: Přerušení, V/V operace |

Virtuální paměť

V paměti: 1MB rámec 0 rámec 1 rámec 2 rámec 3 . . . rámec 255

Rámec (Frame) je stejně

veliký prostor

jako stránka (Page) = 4k

Na disku: 4GB stránka 0 stránka 1 stránka 2 stránka 3 stránka 4 . . . stránka 1M-1

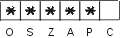

Každý odkaz na paměť obsahuje virtuální adresu:

Ta se transformuje

přes tabulku

obsazení rámců

na reálnou adresu

|

Následující: Vyrovnávací (cache) paměť Obsah |

P000 Architektura počítačůObsahPředchozí: Virtuální paměť |

Vyrovnávací (cache) paměť

0 1 2 . . . 7

<=>

A B

<=>

Procesor

Operační paměť

>MBRychlá

vyrovnávací

paměť

(cache)

2-64kBBloky stejné

velikosti

např. 128 B

Problémy:

- Není nutné vždy přepisovat blok

z VP zpět do OP

- Který blok při zaplňení VP

vyhodit ?

(LRU - Least Recently Used)

= nejdéle nepoužívaný

|

Následující: Realizace LRU Obsah |

P000 Architektura počítačůObsahPředchozí: Vyrovnávací (cache) paměť |

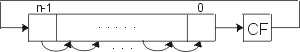

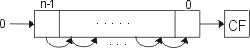

Realizace LRU

a) VP vybavit každý blok čítačem, který se při:

- volání daného bloku nuluje

- volání jiného bloku inkrementuje o jedničku

v případě potřeby se vyřadí blok s nejvyšší hodnotou

př. bloky: 1 2 3 4 volání: 1 0 1 1 2 1 0 2 3 2 0 3 4 3 1 0

bl.2 bl.3 bl.3 bl.4

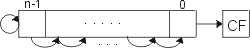

b) Pomocí neúplné matice s prvky nad hlavní diagonálou

- každý prvek je jednobitová pamět- pří volání bloku i se:

- jedničkuje i -tý řádek

- nuluje i -tý sloupec

- nejdéle nepoužité paměťové místo má:

- v řádku nuly

- ve sloupci jedničky

př. 6 5 4 3 2 1

1 2 3 4 5 6

pořadí volání:

2, 5, 6, 1, 3, 4

|

Následující: Další problémy při použití cache paměti Obsah |

P000 Architektura počítačůObsahPředchozí: Realizace LRU |

Další problémy při použití cache paměti

3) Napojení OP na VP a na kanál

operační

paměť

cache

procesor

kanál

4) V multiprocesorových systémech při

sdílení jedné paměti více procesory

|

Následující: Architektura procesoru Intel 8086 Obsah |

P000 Architektura počítačůObsah

|

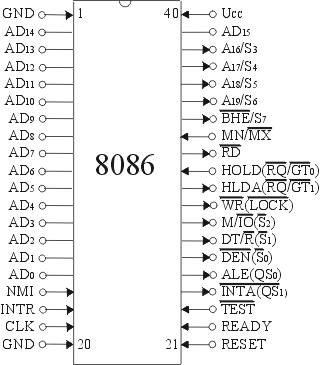

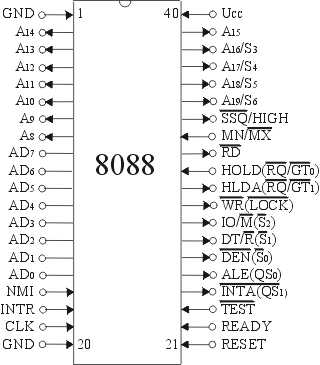

Zapojení procesorů 8086/88

| INTR | Signál žádosti o maskovatelné přerušení. |

|

Signál testovatelný instrukcí WAIT.

Při  =L program pokračuje další instrukcí. =L program pokračuje další instrukcí.

|

| NMI | Signál nemaskovatelného přerušení. |

| RESET | Signál okamžitě ukončující aktivitu CPU a předávající řízení instrukci na adrese 0FFFF0h. |

|

Uzamčení sběrnice pro procesor, který nastavil

=L instrukčním prefixem LOCK. =L instrukčním prefixem LOCK. |

|

Rozlišuje, zda adresa patří paměti nebo V/V v procesoru 8086. |

| Následující:

Typy dat zpracovávané procesory Intel Obsah |

P000 Architektura počítačůObsah

|

Typy dat zpracovávané procesory Intel

Rozsahy zobrazení

| Se znaménkem | Bez znaménka | |

| Slabika | <-128, +127>10 | <0, 255>10 |

| 16bitové slovo | <-32 768, +32 767>10 | <0, 65 535>10 |

| 32bitové slovo | asi (-2.109, +2.109)10 | asi (0, 4.109)10 |

Další zpracovávané typy dat:

| Následující:

Adresace paměti procesoru 8086 Obsah |

P000 Architektura počítačůObsah

|

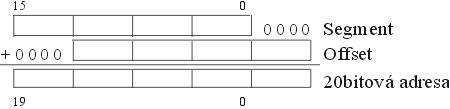

Adresace paměti procesoru 8086

Procesor 8086 pro uložení segmentu poskytuje čtyři 16bitové segmentové registry:

| Následující:

Registry procesoru 8086 Obsah |

P000 Architektura počítačůObsah

|

Registry procesoru 8086

Implicitní přiřazení segmentových registrů

| Při přístupu k | se použije registr | Operace |

| instrukcím | CS (Code Segment) | Výběr operačního kódu nebo přímého operandu. |

| zásobníku | SS (Stack Segment) | Při všech přístupech k zásobníku nebo ve spojitosti s registrem BP. |

| datům | DS (Data Segment) | Při všech přístupech k datům v paměti vyjma zásobníku a přímých operandů. V řetězcových operacích segmentuje zdrojový operand. |

| alternativním datům | ES (Extra Segment) | V řetězcových operacích pro segmentování cílového operandu. |

| Registr s offsetem | Implicitně použitý segmentový registr |

| SP | SS |

| BP | SS |

| BX | DS |

| SI | DS |

| DI | DS (ES v řetězcových operacích) |

| BP v kombinaci s SI nebo DI | SS |

| BX v kombinaci s SI nebo DI | DS |

Explicitní přiřazení segmentového registru offsetovému lze zadat např.:

| Následující:

Příznakový registr 8086 Obsah |

P000 Architektura počítačůObsah

|

Příznakový registr 8086

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| OF | DF | IF | TF | SF | ZF | AF | PF | CF |

| CF | (Carry Flag) obsahuje přenos z nejvyššího bitu, a to jak při práci s 8 nebo 16 bitovým operandem. |

| PF | (Parity Flag) se nastaví na jedničku, pokud dolní osmice bitů výsledku právě provedené operace obsahuje sudý počet "1"(sudá parita výsledku). |

| AF | (Auxiliary Carry Flag) je rozšířením příznaku CF pro přenos přes hranici nejnižší půlslabiky operandu (vždy z bitu 3 do 4 bez ohledu na šířku operandu). Má význam v BCD aritmetice. |

| ZF | (Zero Flag) je nastaven při nulovém výsledku operace. |

| SF | (Sign Flag) je kopií znaménkového bitu výsledku operace. |

| OF | (Overflow Flag) se nastaví na jedničku, pokud při právě dokončené operaci došlo k aritmetickému přeplnění(výsledek spadá mimo rozsah zobrazení). |

| TF | (Trap Flag) uvádí procesor do krokovacího režimu, ve kterém je po provedení první instrukce generováno přerušení(INT 1). Příznak lze nastavit pouze přes zásobník instrukcí IRET. |

| IF | (Interrupt Enable Flag) nulový zabrání uplatnění vnějších maskovatelných přerušení (generovaných signálem INTR). |

| DF | (Direction Flag) řídí směr zpracovávání řetězcových operací. |

| Následující:

Zásobník Obsah |

P000 Architektura počítačůObsah

|

Zásobník

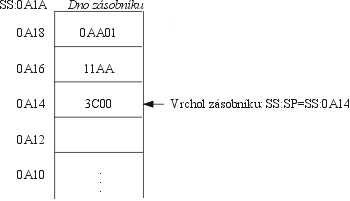

Zásobník procesor implementuje jako strukturu LIFO kdekoli v operační paměti. Všechny odkazy na zásobník jsou segmentovány přes registr SS.

Příklad: Dno zásobníku je na adrese SS:0A1A. Zásobník byl do současného stavu naplněn posloupností instrukcí, které zapsaly hodnoty: 0AA01, 11AA, 3C00.

Výběr a zápis do zásobníku řídí registr SP (Stack Pointer), který obsahuje adresu právě zapsané položky.

Instrukce PUSH provede činnosti v následujícím pořadí:

Instrukce POP provede tyto akce:

Procesor 8086 nemá žádný prostředek, kterým by hlídal maximální naplnění zásobníku.

| Následující:

Přerušení v 8086 Obsah |

P000 Architektura počítačů |

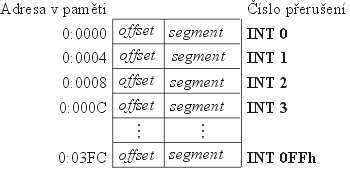

Přerušení v 8086

Vnější (generována technickými prostředky)Vektor adres rutin obsluhujících přerušení

| Následující:

Rezervovaná přerušení 8086, počáteční nastavení

procesoru Obsah |

P000 Architektura počítačůObsah

|

Rezervovaná přerušení 8086

| INT n | Význam |

| 0 1 2 3 4 |

Celočíselné dělení nulou (Divide by Zero) Krokovací režim (Single-Step) Nemaskovatelná přerušení (NMI) Ladící bod (Breakpoint Trap) Přeplnění (Overflow Trap) |

| INT 0 | nastane při dělení nulou v instrukcích DIV a IDIV. Obsah CS:IP uložený do zásobníku ukazuje za (v 80286 a vyšších na) instrukci, která přerušení způsobila. |

| INT 1 | nastane po provedení instrukce, je-li TF=1. |

| INT 2 | se vygeneruje po přijetí signálu NMI (v 8086 pouze chyba parity v paměti), který nelze zakázat nulovou hodnotou příznaku IF. |

| INT 3 | se používá společně s přerušením INT 1 v ladících systémech. Přerušení 03h se vygeneruje po dekódování speciální jednoslabikové instrukce INT 3 (s operačním kódem 0CCh). Přerušení uloží do zásobníku obsah CS:IP ukazující na slabiku bezprostředně za touto instrukcí. |

| INT 4 | provede instrukce INT 0(Interrupt on Overflow), je-li v okamžiku jejího dekódování nastaven příznak OF=1. CS:IP ukazuje na slabiku za touto instrukcí. |

Počáteční nastavení procesoru

| Registr | Obsah |

| Příznakový registr IP DS, ES, SS CS |

0 0 0 0FFFFh |

| Následující:

Adresovací techniky Obsah |

P000 Architektura počítačůObsah

|

Adresovací techniky

Instrukce:

| Příklad | |

| Registr | MOV AH,BL | |

| Přímý operand | MOV AH,50 | |

| Přímá adresa | PROM | DB ? |

| (totožné s MOV AH,[PROM]) | MOV AH,PROM | |

| nebo | MOV AH,DS:[101] | |

| Nepřímá adresa (SI, DI, SP, BP, BX) | MOV AH,[BX] | |

| Bázovaná adresa (BP, BX) | MOV AH,[BP+PROM] | |

| Indexovaná adresa (SI, DI) | MOV AH,[PROM+SI] | |

| nebo | MOV AH, PROM[SI] | |

| Báze + Index (BP, BX + SI, DI) | MOV AH,[BX][DI] | |

| nebo | MOV AH,[BP+DI] | |

| Přímá + Báze + Index | MOV AH,PROM[BX][DI] | |

| nebo | MOV AH,[PROM+BX+DI] | |

| nebo | MOV AH,[PROM+BX+DI+1] |

| Následující:

Instrukce MOV Obsah |

P000 Architektura počítačůObsah

|

Instrukce MOV

Instukce MOV příznaky nemění!!| MOV r/m8,r8 | MOV AL,BL | AL:=BL |

| MOV Slabika,CH | Slabika:=CH | |

| MOV r/m16,r16 | MOV BX,CX | |

| MOV r8,r/m8 | ||

| MOV r16,r/m8 | ||

| MOV r/m16,segmentový registr | MOV AX,CS | |

| MOV segmentový registr,r/m16 | MOV DS,AX | |

| Nelze MOV CS,.. !!! | ||

| MOV r/m8,imm8 | MOV Slabika,10 | |

| MOV r/m16,imm16 |

| Následující:

Aritmetické instrukce Obsah |

P000 Architektura počítačůObsah

|

Aritmetické instrukce (celočíselné)

| ADD | r/m8,imm8 | ADD AL,80 | AL:=AL+80 |

|

ADD Slabika,-10 | ||

| r/m16,imm16 | ADD CX,10000 | ||

| r/m16,imm8 | ADD CX,10 | <-rozšíření s respektováním znaménka | |

| r/m8,r8 | ADD CH,CL | ||

| r/m16,r16 | ADD AX,BX | ||

| r8,r/m8 | |||

| r16,r/m16 | |||

| ADC | ADD WITH CARRY | ||

| ADC AL,CL | AL:=AL+CL+CF | ||

| SUB | SUBTRACTION | ||

| SUB AL,CL | AL:=AL-CL | ||

| SBB | SUBTRACTION WITH BORROW | ||

| SBB AL,CL | AL:=AL-CL-CF | ||

| CMP | COMPARE | ||

| CMP AL,CL | F:=AL-CL | ||

| INC | INCREMENT | ||

|

INC r/m8 | INC Slabika | Slabika:=Slabika+1 |

| INC r/m16 | INC DX | ||

| DEC | DECREMENT | ||

| DEC Slabika | Slabika:=Slabika-1 | ||

| NEG | DVOJKOVÝ DOPLŇEK | ||

|

NEG Slabika | Slabika:= -Slabika | |

| CBW | CONVERT BYTE TO WORD | ||

|

CBW | AX:=AL se zachováním znaménka. | |

| CWD | CONVERT WORD TO DOUBLEWORD | ||

| CWD |  |

||

| IMUL | SIGNED MULTIPLICATION | respektuje znaménka! | |

|

IMUL r/m8 | IMUL BL | AX:=AL * BL |

| IMUL Slabika | AX:=AL * Slabika | ||

| IMUL r/m16 | IMUL CX | DX&AX:=AX * CX | |

| IMUL Slovo | DX&AX:=AX * Slovo | ||

| MUL | UNSIGNED MULTIPLICATION | ||

| Neuvažuje znaménkový bit, jinak stejné jako IMUL | |||

| IDIV | SIGNED DIVIDE | ||

|

IDIV r/m8 | IDIV BL | AL:=AX BL BLAH:=AX modulo BL |

| IDIV Slabika | AL:=AX Slabika SlabikaAH:=AX modulo Slabika |

||

| IDIV r/m16 | IDIV CX | AX:=DX&AX CX CXDX:=DX&AX modulo CX |

|

| IDIV Slovo | AX:=DX&AX Slovo SlovoDX:=DX&AX modulo Slovo |

||

| Je-li podíl větší než maximální rozsah zobrazení -> INT 0 Zbytek má stejné znaménko jako dělenec. |

|||

| DIV | UNSIGNED DIVIDE | ||

| Neznaménkové | |||

| Následující:

Logické instrukce Obsah |

P000 Architektura počítačůObsah

|

Logické instrukce

| AND | LOGICKÝ SOUČIN PO BITECH | ||

| kombinace parametrů viz "ADD" | AND AL,7 AND Slovo,1FFFh |

AL:=AL /\ 7 Slovo:=Slovo /\ 1FFFh |

| OR | LOGICKÝ SOUČET | ||

| OR AL,7 | AL:=AL \/ 7 | ||

| XOR | NONEKVIVALENCE | ||

| XOR AL,7 | AL:=AL  7 7 |

||

| NOT | INVERZE BITů (JEDNIČKOVÝ DOPLNĚK) | ||

| NOT r/m 8 | NOT AH NOT Slab |

AH:=  Slab:=  |

| NOT r/m16 | NOT SI NOT Slovo |

SI:=  Slovo:=  |

|

| TEST | LOGICAL COMPARE | ||

| TEST r/m8,imm8 | TEST AL,7 TEST Slab,15 |

F:=AL /\ 7 F:=Slab /\ 15 |

| TEST r/m16,imm16 TEST r/m8,r8 TEST r/m16,r16 |

| Následující:

Rotace, posuvy Obsah |

P000 Architektura počítačůObsah

|

Rotace

| ROL | ROTATE LEFT | |

| ROL r/m8,1 ROL r/m8,CL ROL r/m16,1 ROL r/m16,CL |  |

|

| 8086 : CL neomezeno 286,.. : CL /\ 1Fh | ||

| OF je definováno pouze při rotaci o 1 bit: | ||

| ROL: | OF:=CF  bitn-1 bitn-1tj. OF se nastaví, pokud se hodnota CF nerovná novému nejvyššímu bitu. | |

| ROR | ROTATE RIGHT | |

|

||

| ROR: | OF:=bitn-1  bitn-2 bitn-2 |

|

| ROL | ROTATE LEFT THROUGH CARRY | |

|

||

| RCR | ROTATE RIGHT THROUGH CARRY | |

|

||

Posuvy

| SAL SHL |

SHIFT ARITHMETIC LEFT SHIFT LOGICAL LEFT |

Obě provedou Obě provedoututéž akci. |

| Varianty viz instrukce "ROL" |  |

| znaménko aritmetického násobení 2n OF:=CF |

||

| SAR | SHIFT ARITHMETIC RIGHT | |

| OF:=0 |  |

|

| SHR | SHIFT LOGICAL RIGHT | |

| OF:=původní bitn-1 |  |

| Následující:

Větvení programu Obsah |

P000 Architektura počítačůObsah

|

Větvení programu

JMP JUMP=NEPODMÍNĚNÝ SKOK

| JMP rel8 | JMP SHORT návěští | krátký skok IP:=IP+vzdálenost návěští |

| JMP rel16 | JMP návěští | blízký skok IP:=IP+vzdálenost návěští |

| JMP ptr16:16 | JMP FAR_PTR návěští | vzdálený skok CS:IP:= segment:offset návěští |

| JMP r/m16 | JMP [BX] JMP [slovo] |

nepřímý blízký skok IP:=BX IP:=slovo |

| JMP m16:16 | JMP [dvojslovo] | CS:IP:=dvojslovo nepřímý skok vzdálený |

| Následující:

Podmíněné skoky Obsah |

P000 Architektura počítačůObsah

|

Podmíněné skoky

JUMPS CONDITIONAL| JUMP SHORT IF.. | TESTOVANÁ PODMÍNKA |

VÝSLEDEK POSLEDNÍ OPERACE |

|

| JE JZ |

EQUAL EQUALZERO |

ZF=1 | roven nulový |

| JNE JNZ |

NOT EQUAL NOT ZERO |

ZF=0 | různý nenulový |

| JP JPE |

PARITY PARITY EVEN |

PF=1 | sudá parita |

| JNP JPO |

NOT PARITY PARITY ODD |

PF=0 | lichá parita |

| JS | SIGNUM | SF=1 | záporný |

| JNS | NOT SIGNUM | SF=0 | kladný \/ nulový |

| JC | CARRY | CF=1 | nastal přenos |

| JNC | NOT CARRY | CF=0 | nenastal přenos |

| JO | OVERFLOW | OF=1 | nastalo přetečení |

| JNO | NOT OVERFLOW | OF=0 | nenastalo přetečení |

| JB JNAE |

BELOW NOT ABOVE NOR EQUAL |

CF=1 | nz. menší |

| Příklad: |  +2 : 0 1 0 +2 : 0 1 0+5 : 1 0 1 |

nz. |

CMP 2,5 0 1 0 ZF=0

- 1 0 1 OF=1

nz. 2<5 1 1 0 1 SF=1

CF=1 |

| JL JNGE |

LESS NOT ABOVE NOR EQUAL |

SF  OF OF |

z. menší |

| Příklad: |  +2 : 0 1 0 +2 : 0 1 0-3 : 1 0 1 |

z. | CMP 2,-3 z: 2 |

| JA JNBE |

ABOVE NOT BELOW NOR EQUAL |

(CF=0) /\ (ZF=0) | nz. větší |

| JG JNLE |

GREATER NOT LESS NOR EQUAL |

(SF=OF) /\ (ZF=0) | z. větší |

| JBE JNA |

BELOW OR EQUAL NOT ABOVE |

(CF=1) \/ (ZF=1) | nz. menší nebo rovno |

| JLE JNG |

LESS OR EQUAL NOT GREATER |

(SF  OF) \/ (ZF=1) OF) \/ (ZF=1) |

z. menší nebo rovno |

| JAE JNB |

ABOVE OR EQUAL NOT BELOW |

CF=0 | nz. větší nebo rovno |

| JGE JNL |

GREATER OR EQUAL NOT LESS |

SF=OF | z. větší nebo rovno |

| JCXZ | JUMP SHORT IF CX=0 používá se pro řízení cyklů |

||

| Jpodm rel8 | JZ návěští | krátký skok na návěští je-li ZF=1, jinak se pokračuje následující instrukcí. | |

| JCXZ rel8 | JCXZ návěští | krátký skok na návěští je-li CX=0 | |

| Následující:

Zásobník Obsah |

P000 Architektura počítačůObsah

|

Zásobník

| PUSH | Uložení 16bitového objektu do zásobníku: | |

| 1) SP:=SP-2 | ||

| 2) [SS:SP]:=operand_16bitový | ||

| PUSH m16 PUSH r16 PUSH segment |

PUSH slovo PUSH AX PUSH CS |

|

| POP | Výběr 16bitového objektu ze zásobníku: | |

| 1) pomocná:=[SS:SP] 2) SP:=SP+2 3) operand_16bitový:=pomocná |

||

| POP m16 POP r16 POP segment |

POP slovo POP BX NELZE: POP CS !!! |

|

| POP SS | zakazuje přerušení na dobu provedení této a následujcí instrukce | |

8086: SP=6 !!! 80286,... SP=6 !!!

PUSH SP SP:=6-2=4 PUSH SP SP:=6-2=4

[4]:=4 [4]:=6

POP SP POM:=[4]=4 POP SP POM:=[4]=6

SP:=4+2=6 SP:=4+2=6

SP:=POM=4 SP:=POM=6

SP=4 !!! SP=6 !!!

V 8086 dává posloupnost V 80286,... "PUSH SP" ukládá SP

instrukcí "PUSH SP" a do zásobníku nesnížené o 2 !!

"POP SP" špatný výsledek !!

| Následující:

Volání a návrat z podprogramu Obsah |

P000 Architektura počítačů |

Volání a návrat z podprogramu

| CALL | |||

| CALL rel16 CALL ptr16:16 CALL r/m16 CALL m16:16 |

CALL návěští CALL FAR PTR návěští CALL [BX] CALL [dvojslovo] |

IP:=IP+vzdálenost návěští CS:IP:=ptr 16:16 IP:=BX CS:IP := dvojslovo |

|

| CALL: | 1) PUSH CS - pouze "FAR" varianta 2) PUSH IP+délka_instrukce 3) (CS):IP := operand |

||

| RET | RETURN | ||

| RET | POP IP | blízký návrat | |

| RETF | POP IP POP CS |

vzdálený návrat | |

| RET imm16 | POP IP SP:=SP+imm16 |

||

| RETF imm16 | POP IP POP CS SP:=SP+imm16 |

||

| Příklad: |

|

návrat z podprogramu s odstraněním 1 slova | |

| Následující:

Příznakový registr Obsah |

P000 Architektura počítačůObsah

|

Příznakový registr

| PUSHF | PUSH FLAG REGISTER | nemění příznaky | |

| PUSHF | uloží 16bitový registr F | ||

| POPF | POP FLAG REGISTER | mění příznaky | |

| POP F | vybere 16bitový objekt a uloží jej do F | ||

| STI STD STC CLI CLD CLC |

IF:=1 DF:=1 CF:=1 IF:=0 DF:=0 CF:=0 |

povolení přerušení řetězce odzadu zákaz přerušení řetězce odpředu |

|

| Poznámka: STI povolí přerušení až po provedení následující instrukce. | |||

| CMC | CF:= |

||

| LAHF | LOAD FLAGS INTO AH | ||

| LAHF | AH := bity 0-7 FLAGS | ||

| SAFH | STORE AH INTO FLAGS | ||

| SAHF | bity 0-7 FLAGS := AH | ||

| Následující:

Přerušení Obsah |

P000 Architektura počítačůObsah

|

Přerušení

| INT | INTERRUPT | |

| INT imm8 | délka 2 slabiky | |

| 1) PUSHF 2) IF:=0, TF:=0 3) PUSH CS 4) CS:=[imm8 x 4 + 2] 5) PUSH IP + délka instrukce (obsah zásobníku ukazuje za "INT imm8"!) 6) IP:=[imm8 x 4] |

||

| INT 3 | ||

| délka 1 slabika, operační kód: 0CCh | ||

| INT 0 | INTERRUPT IF OVERFLOW | |

| délka 1 slabika, operační kód 0CEh provede INT 4, je-li OF=1 |

||

| IRET | INTERRUPT RETURN | |

| 1) POP IP 2) POP CS 3) POP F |

| Následující:

Cykly Obsah |

P000 Architektura počítačů |

Cykly

| LOOP | UNCONDITIONAL LOOP | nemění příznaky |

| registr CX ... čítač průchodů | ||

| Příklad: | MOV CX, počet_průchodů OPAKUJ: . . . LOOP OPAKUJ zde, je-li CX=0 |

inicializace řídící proměnné tělo cyklu CX:=CX-1 pokud CX  0 ... SHORT skok na OPAKUJ 0 ... SHORT skok na OPAKUJ |

| LOOP rel8 | LOOP OPAKUJ | 1) CX:=CX-1 2) je-li CX  0 ... SHORT skok 0 ... SHORT skok |

| CONDITIONAL LOOP | ||

LOOPE LOOPELOOPZ |

LOOPE rel8 | 1) CX:=CX-1 2) je-li (CX  0)

/\ (ZX=1) ... SHORT skok na rel8 0)

/\ (ZX=1) ... SHORT skok na rel8 |

LOOPNE LOOPNELOOPNZ |

LOOPNE rel8 | 1) CX:=CX-1 2) je-li (CX  0)

/\ (ZX=0) ... SHORT skok na rel8 0)

/\ (ZX=0) ... SHORT skok na rel8 |

| Následující:

Ovládání V/V Obsah |

P000 Architektura počítačů |

Ovládání V/V

| IN | INPUT FROM PORT | |

| Přenos slabiky nebo slova ze V/V brány do registru AL nebo AX. | ||

| IN AL, imm8 IN AX, imm8 IN AL, DX IN AX, DX |

číslo V/V brány:

|

|

16bitový přenos: |

imm8, imm8+1 DX, DX+1 |

|

| OUT | OUTPUT TO PORT | |

| Přenos slabiky nebo slova z registru AL nebo AX do V/V brány. | ||

| OUT imm8, AL OUT imm8, AX OUT DX, AL OUT DX, AX |

||

| Následující:

Další instrukce přesunů dat Obsah |

P000 Architektura počítačůObsah

|

Další instrukce přesunů dat

| XCHG | cílový, zdrojový | ... zamění obsahy | |

| XCHG r/m8, r8 XCHG r8, r/m8 XCHG r/m16, r16 XCHG r16, r/m16 |

XCHG AL, AH XCHG AX, slovo |

||

| XLAT | provede | AL:=DS:[BX+AL] | |

| LEA | r16, imm16 | ||

| totožné s: MOV r16, offset .... MOV BX, offset Tabulka = LEA BX, Tabulka |

|||

| LDS | r16, m16:16 | LDS BX, Dvojslovo | DS:BX:= obsah Dvojslovo |

| LES | r16, m16:16 | LES DI, Dvojslovo | ES:DI:= obsah Dvojslovo |

Řídící instrukce

| NOP | NO OPERATION operační kód 90h ekv. XCHG AX, AX | |

| HLT | HALT zastavení procesoru |

|

| ESC | Vzorek uvádějící instrukce 8087. | |

| WAIT | Čekání na dokončení akce 8087. | |

| LOCK | Instrukční prefix "zamykající" sběrnici po dobu trvání instrukce. | |

| Příklad: | LOCK ADD Slovo, DX | Slovo:=Slovo+DX |

| Následující:

Řetězcové instrukce Obsah |

P000 Architektura počítačůObsah

|

Řetězcové instrukce

| MOVSB Slabika | ES:[DI]:=DS:[SI]

|

žádný příznak |

| MOVSW Slovo | ES:[DI]:=DS:[SI]

|

žádný příznak |

| CMPSB/CMPSW | F:=DS:[SI] - ES:[DI] inc/dec SI, DI |

všechny příznaky |

| SCASB/SCASW | F:=AL/AX - ES:[DI] inc/dec DI |

všechny příznaky |

| LODSB/LODSW | AL/AX:=DS:[SI] inc/dec SI |

žádný příznak |

| STOSB/STOSW | ES:[DI]:=AL/AX inc/dec DI |

žádný příznak |

| REP | instrukční prefix pro opakování řetězcových instrukcí | nastaví ZF |

| 1. 2. 3. 4. 5. |

Je-li CX=0 ... konec Uplatněno případné přerušení Jedno provedení instrukce (řetězcové) CX:=CX-1 Je-li REP ... jdi na 1 |

Má význam pouze u CMPS a SCAS |

|

Je-li REPZ (REPE) a je-li ZF=1 ... jdi na 1. Je-li REPNZ (REPNE) a je-li ZF=0 ... jdi na 1. |

Jinak neopakuj = KONEC. |

| Následující:

Instrukce pro podporu BCD aritmetiky Obsah |

P000 Architektura počítačůObsah

|

Instrukce pro podporu BCD aritmetiky

| BCD číslice | 4 bity; 0 - 9 půlslabika (nibble) |

|

| Nezhuštěný tvar | Unpacked Decimal | |

| 1 číslice v dolní půlslabice, horní musí být rovna 0 |

||

| Zhuštěný tvar | Packed Decimal | |

| 2 číslice v jedné slabice | ||

| AAA | Ascii Adjust After Adition | |

| Je-li AF=1 \/ AL>9 => | AH:=AH+1; AL:=AL+6 ; AL1-4:=0; AF:=CF:=1 |

|

| Jinak: AF:=CF:=0 | ||

| AAD | Ascii Adjust AX Before Division |

| Následující:

Zapojení procesoru 80286 Obsah |

Michal Brandejs brandejs@informatics.muni.cz