# VHDL

Zdeněk Matěj 72963@mail.muni.cz

## **VHDL**

- VHSIC (Very High Speed Integrated Circuit)

- Hardware

- Description

- Language

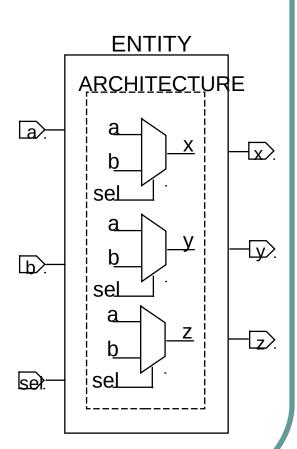

## Structure

- Construction blocks

- Entity

- Describes a module's interface

- Architecture

- Behavioral description of the block

# **Entity**

Describes interface of latch - it's inputs and outputs

Input and output signals are marked with in and out (we can also use inout)

## Architecture

- Represents a behavioral description's instance

- Generally, one entity may have multiple architectures

**architecture** dataflow **of** latch **is –** architecture's name is dataflow **begin**

```

q<=r nor nq; -- operator <= assigns signal

nq<=s nor q; -- function "nor" has been defined

end dataflow;</pre>

```

## Component

We use it for module's instantiation

```

entity latch is

port (s,r: in bit;

q,nq: out bit);

end latch;

architecture structure of latch is

component nor gate

port (a,b: in bit;

c: out bit);

-- make sure you keep the ports' order:- in,in,out

end component;

begin

n1: nor gate

port map (r,nq,q);

-- component ports are assigned to given signals in the parent architecture

n2: nor_gate

port map (s,q,nq);

end structure;

```

# Assignments

- VHDL is strongly typed and there are no automatic type casts like in C language

- Signal

- a<=b and c;</p>

- Variable

- v:=a + 2;

#### Process

It allows us to create a structured description of architecture

```

process (b,c) -- process is executed whenever b or c changes

begin

a<=b xor c;

end process;</pre>

```

## Variables

Used exclusively inside a process block

```

count: process (x)

variable cnt : integer := -1;

begin

cnt:=cnt + 1;

end process;

```

Before first process execution, value of cnt will be initialized as 0

## Variables - cont.

- For data types, we can use integer, bit, etc. (see the documentation)

- However, for signal we use STD\_LOGIC data type

- Example of vector definition: std\_logic\_vector(0 to 17);

## Sequential expressions

Can be created exclusively inside a process

```

count: process (x)

variable cnt : integer :=0 ;

begin

if (x='1' and x'last_value='0') then

cnt:=cnt + 1;

end if;

end process;

```

- last\_value stands for latest value of variable x before invoking the process

- Another sequential constructions can be examinated in the documentation

## Signals

- Signals are local for an architecture and can't be accessed from outside

- All assignments to signals are performed after the whole process body is finished

```

signal x,y,z : bit;

...

process (y) -- change of y starts the process

begin

x<=y;

end process;</pre>

```

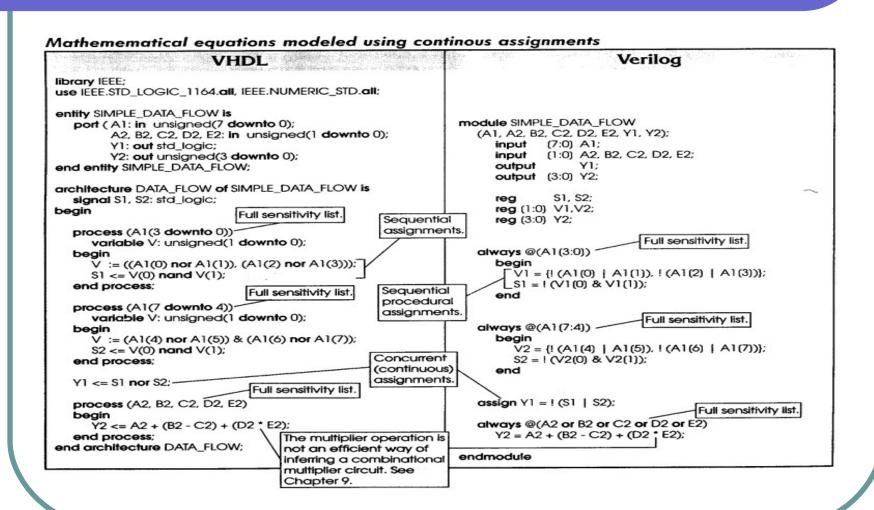

# Comparison of VHDL and Verilog

#### Function calls

```

VHDL

Verilog

library IEEE:

use IEEE.STD_Logic_1164.all;

entity FUNCTION CALLS is

module FUNCTION CALLS

port (S1, S2, A1, B1, C1, D1, A2, B2, C2, D2,

($1.$2, A1,B12,C1,D1,Y1, A2,B2,C2,D2,Y2, A3,B3,C3,D3,Y3);

A3, B3, C3, D3: in std logic;

Y1, Y2, Y3: out std logic);

input $1,$2, A1,B1,C1,D1, A2,B2,C2,D2, A3,B3,C3,D3;

end entity FUNCTION CALLS:

output Y1, Y2, Y3;

reg Y2, Y3;

architecture LOGIC of FUNCTION_CALLS is

function Fn1 (F1, F2, F3, F4: std logic) return std logic is

function Fn1:

variable Result: std logic;

input F1, F2, F3, F4;

begin

Result := (F1 xor F2) or (F3 xnor F4);

Fn1 = ((F1 ^ F2) & ! (F3 ^ F4));

return Result;

end

end Fn1:

endfunction

Positional notation.

Only positional notation allowed in Verilog subprograms calls.

begin

Y1 <= Fn1(A1, B1, C1, D1) or S1 or S2;

assign Y1 = Fn1(A1, B1, C1, D1) | S1 | S2:

process ($1, $2, A1, B1, C1, D1, A2, B2, C2, D2)

always @(S1 or S2 or A2 or B2 or C2 or D2 or A3 or B3 or

begin

C3 or D3)

Named notation.

begin

Y2 <= $1 or $2 or Fn1(F3=>C2, F4=>D2, F1=>A2, F2=>B2);

Y2 = $1 | Fn1(A2, B2, C2, D2) | $2;

Y3 <= $1 or Fn1(A3, B3, F4 => D3, F3 => C3) or $2;

end process:

Y3 = $1 | $2 | Fn1(A3, B3, C3, D3);

Mixed positional & named notation.

end

end architecture LOGIC:

endmodule

```

# Comparison of VHDL and Verilog

## Literature

- https://l202.fi.muni.cz/vyuka/pv200/materialy

- HDL chip design Douglas J. Smith

- Altera: http://www.altera.com/support/examples/vhdl/vhdl.html

- http://esd.cs.ucr.edu/labs/tutorial/

- http://www.angelfire.com/in/rajesh52/verilogvhdl.html

- http://en.wikipedia.org/wiki/VHDL

## Tasks

- Task no. 1

- Describe 4-bit adder in VHDL, use LEDs and SWITCHes

- Task no. 2

- Describe RS circuit in VHDL, use two KEYs and LED to indicate the current state.

- Task no. 3

- Describe clock divider in VHDL in a separate module and use the module's instance in another module (e.g., in top module).

Propagate divided clock signal to a LED.